# ATP SATA3 mSATA Embedded Module Specification

Version 1.0

**ATP Electronics, Inc.**

# CONTENT

| Rev | ision History1                         |

|-----|----------------------------------------|

| 1.0 | ATP mSATA Embedded Module Overview2    |

| 1.1 | ATP Product Image2                     |

| 1.2 | Introduction                           |

| 1.3 | Main Features3                         |

| 2.0 | Product Specification                  |

| 2.1 | Block Diagram5                         |

| 2.2 | Environment Specifications5            |

| 2.3 | IOPS Performance                       |

| 2.4 | Maximum Read/Write Performance6        |

| 2.5 | Electrical Characteristics             |

| 2.6 | Reliability6                           |

| 2.7 | Write/Erase Endurance <sup>1</sup> 7   |

| 2.8 | Certification and compliance7          |

| 3.0 | SATA SSD Pin Assignment8               |

| 3.1 | Pin Location8                          |

| 3.2 | Pin Assignment8                        |

| 4.0 | Command Set                            |

| 4.1 | ATA Command Set10                      |

| 4.2 | Identity Device Data12                 |

| 4.3 | Smart Information15                    |

| 4.4 | SMART Command Transport19              |

| 4.5 | Set Features19                         |

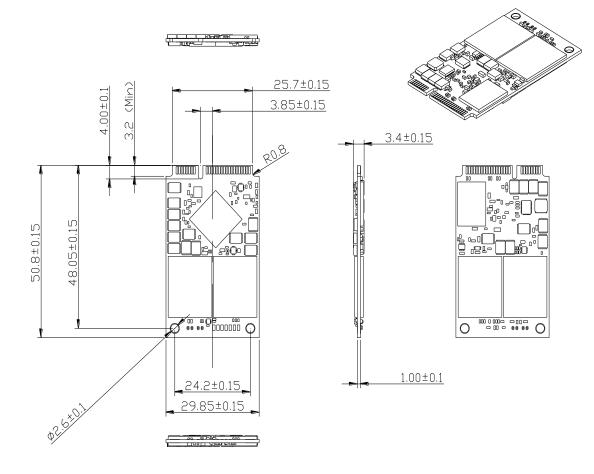

| 5.0 | Mechanical Information19               |

| 5.1 | Physical Dimension Specifications19    |

| 5.2 | Mechanical Form Factor (Units in mm)20 |

# **ATP Electronics, Inc.**

# Disclaimer

ATP Electronics Inc. shall not be liable for any errors or omissions that may appear in this document, and disclaims responsibility for any consequences resulting from the use of the information set forth herein.

ATP may make changes to specifications and product descriptions at any time, without notice. The information in this paper is furnished for informational use only so ATP assumes no responsibility or liability for any errors or inaccuracies that may appear in this document.

All parts of the ATP documentation are protected by copyright law and all rights are reserved. This documentation may not, in whole or in part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine-readable form without prior consent, in writing, from ATP Electronics, Inc.

The information set forth in this document is considered to be "Proprietary" and "Confidential" property owned by ATP.

© Copyright ATP All rights reserved.

# **Revision History**

| Date                         | Version | Revision History  |

|------------------------------|---------|-------------------|

| Jan. 12 <sup>th</sup> , 2016 | 1.0     | - New BOM Release |

# **1.0 ATP mSATA Embedded Module Overview**

# 1.1 ATP Product Image

Figure 1-1: ATP Product Image (reference only)

## Table 1-1: Capacities

| ATP P/N          | CAPACITY |

|------------------|----------|

| AF16GSMHI-VADXP  | 16GB     |

| AF32GSMHI-VADXP  | 32GB     |

| AF64GSMHI-VACXP  | 64GB     |

| AF128GSMHI-VACXP | 128GB    |

| AF256GSMHI-VAAXP | 256GB    |

| AF512GSMHI-VAAXP | 512GB    |

Note: GB = 1,000,000,000 Byte

### **1.2** Introduction

The ATP mSATA Embedded Module is a high performance and high capacity mass storage solution in Slim form factor. Utilizing MLC (Multi-Level Cell) NAND Flash components provides outstanding performance and proven reliability for products operating.

ATP mSATA Embedded Module is perfect for thin devices, especially networking, thin clients, embedded appliance, and also suitable for industrial applications such as transportation, industrial PC, healthcare, telecommunications, and other harsh environments where data integrity and consistent performance is mission critical.

### 1.3 Main Features

- Capacity: 16GB~512GB

- MLC (Multi-Level Cell) NAND flash memory

- Operating temperature:  $0^{\circ}$ C to  $70^{\circ}$ C

- Maximum performance: Sequential read up to 530 MB/s, sequential write up to 440 MB/s

- JEDEC standard: MO-300A

- Compliant with Serial ATA Revision 3.2

- SATA 6.0Gbps interface and backward compatible with 1.5Gbps and SATA 3Gbps interface rate

- Hardware BCH ECC, correct up to 60-bit ECC per 1024 bytes of data

- SMART function support by ATA CMD

- Enhanced endurance by Global wear-leveling

- AutoRefresh, automatic data protection in read operation

- PowerProtector Gen.2, data integrity under power-cycling

- CE, FCC certification

#### **PowerProtector – Power Cycling Protection**

The unstable power conditions of outdoor applications such as transportation, telecommunications/networking and embedded systems run the risk of data loss and drive corruption during a sudden power failure.

A standalone hardware design is the ideal configuration for power backup, ensuring a sufficient amount of reserve power during any power abnormalities and minimizing the consequent host re-designs for adding new features. During a sudden power failure, the abnormality is discovered by a power loss detection circuit and activates the power protection mechanism. The device then draws power from power protection reservoir, where the reserve power is stored. The reserve power gives enough time for the flash device to conclude the last writing command without losing any data.

### AutoRefresh Technology – Data Integrity Protection

Over time the error bits accumulate to the threshold in the flash memory cell and eventually become uncorrectable despite using the ECC engine. In the traditional handling method, the data is moved to a different location in the flash memory; despite the corrupted data is beyond repaired before the transition.

The situation is worse in frequent read applications, such as navigation systems or OS boot-up devices. The map or operation system is preloaded into the storage media and there may be one time write and following by read operation only. Read disturbance is the result of electrical interference from multiple read operations in surrounding pages. After NAND flash accumulates 100,000 read cycles, uncorrectable ECC errors may occur in the affected pages which results in data failure in the same block.

To prevent data corruption, ATP memory product monitors the error bit levels in each read operation; when it reaches the preset threshold value, AutoRefresh is activated by programming the data into another block before the data is corrupted. After the re-programming operation is completed, the controller reads the data and compares the data/parity to ensure data integrity.

Owing to different user experiences, please contact ATP for AutoRefresh in real applications.

# 2.0 Product Specification

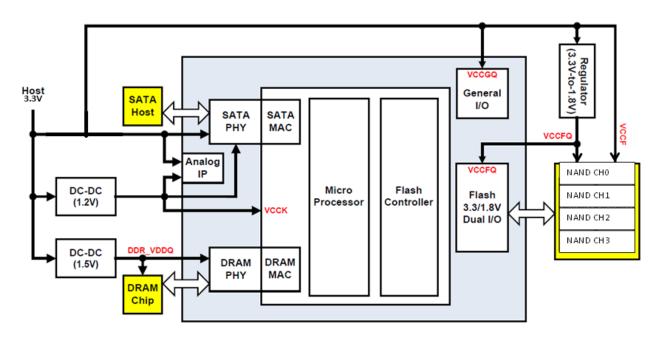

### 2.1 Block Diagram

ATP mSATA Embedded Module consists of below functional blocks. The advanced

architecture is optimized to provide highest data reliability and transfer performance.

### 2.2 Environment Specifications

Table 2-1

| Туре        |               | Standard                       |

|-------------|---------------|--------------------------------|

| Tomporatura | Operating     | 0°C to 70°C                    |

| Temperature | Non-Operating | -40°C to 85°C                  |

| Humidity    | Operating     | 25°C, 8% to 95%, noncondensing |

| Humaity     | Non-Operating | 40°C, 8% to 93%, noncondensing |

| Vibration   | Non-Operating | sine 16.4G, 10~2000Hz          |

| Shock       | Non-Operating | Half sine 1500G/0.5ms          |

| Altitude    | Operating     | 80,000 feet Max.               |

| Annuae      | Non-Operating | 80,000 feet Max.               |

### 2.3 IOPS Performance

### Table 2-2

| Туре                | Value             |

|---------------------|-------------------|

| 4K Random Read IOPS | Up to 72,040 IOPS |

Note: Input/Output operations per second tested by Crystal Disk Mark on 512GB device.

#### 2.4 Maximum Read/Write Performance

| Table 2-3    |                        |      |      |      |       |       |       |  |

|--------------|------------------------|------|------|------|-------|-------|-------|--|

|              | Туре                   | 16GB | 32GB | 64GB | 128GB | 256GB | 512GB |  |

| Crystal Disk | Sequential Read (MB/s) | 110  | 220  | 400  | 520   | 520   | 530   |  |

| Mark         | Sequential Write(MB/s) | 20   | 40   | 75   | 130   | 260   | 440   |  |

- -

### **2.5 Electrical Characteristics**

| Table 2-4      |                 |      |     |      |      |        |

|----------------|-----------------|------|-----|------|------|--------|

| Parameter      | Symbol          | Min  | Тур | Max  | Unit | Remark |

| Supply voltage | V <sub>CC</sub> | 3.15 | 3.3 | 3.45 | V    |        |

### Table2-5

| Parameter             | Symbol         | Min  | Тур  | Max  | Unit | Remark    |

|-----------------------|----------------|------|------|------|------|-----------|

| Sustained write power | Pw             | 0.50 | 3.80 | 5.65 | W    | RMS value |

| Sustained read power  | P <sub>R</sub> | 0.50 | 1.65 | 2.75 | W    | RMS value |

| Idle power            | Ps             | 0.30 | 0.35 | 0.45 | W    | RMS value |

### 2.6 Reliability

| Table2-6                   |                              |  |  |  |

|----------------------------|------------------------------|--|--|--|

| Туре                       | Value                        |  |  |  |

| MTBF (@ 25°C) <sup>1</sup> | 2,000,000 hours              |  |  |  |

| Data Retention (@ 55°C)    | 5 years (with 10% P/E cycle) |  |  |  |

. .

Notes: The Mean Time between Failures (MTBF) is calculated using a prediction methodology, Telcordia SR-332, which based on reliability

data of the individual components in the mSATA. It assumes nominal voltage, with all other parameters within specified range.

# 2.7 Write/Erase Endurance<sup>1</sup>

Table 2-7

| Туре                 | Value                                            |  |  |  |

|----------------------|--------------------------------------------------|--|--|--|

|                      | Enhanced global dynamic and static wear-leveling |  |  |  |

| Endurance Technology | algorithm                                        |  |  |  |

|                      | MLC Flash block: 3,000 P/E cycles                |  |  |  |

|                      | 16GB: 6.85 TB Random write                       |  |  |  |

|                      | 19.2 TB Sequential write                         |  |  |  |

|                      | 32GB: 13.71 TB Random write                      |  |  |  |

|                      | 38.4 TB Sequential write                         |  |  |  |

|                      | 64GB: 27.43 TB Random write                      |  |  |  |

| SSD Endurance        | 76.8 TB Sequential write                         |  |  |  |

| SSD Endurance        | 128GB: 54.86 TB Random write                     |  |  |  |

|                      | 153.6 TB Sequential write                        |  |  |  |

|                      | 256GB: 109.7 TB Random write                     |  |  |  |

|                      | 307.2 TB Sequential write                        |  |  |  |

|                      | 512GB: 219.43 TB Random write                    |  |  |  |

|                      | 614.4 TB Sequential write                        |  |  |  |

Note:

- Endurance for the mSATA can be predicted based on the usage conditions applied to the device, the internal NAND component cycles, the write amplification factor, and the wear leveling efficiency of the drive. TBW may vary depending on application, please contact ATP for TCO evaluation if specific usage type applies.

- 2. The random endurance is based on JEDEC219 enterprise workload.

### 2.8 Certification and compliance

Table 2-9

| Mark/Approval | Certification                                                             |     |  |  |  |  |

|---------------|---------------------------------------------------------------------------|-----|--|--|--|--|

|               | The CE marking (also known as CE mark) is a mandatory <u>conformance</u>  |     |  |  |  |  |

|               | mark on many products placed on the single market in the European         |     |  |  |  |  |

| ( (           | Economic Area (EEA). The CE marking certifies that a product has met      | Yes |  |  |  |  |

|               | EU consumer safety, health or environmental requirements. CE stands       |     |  |  |  |  |

|               | for Conformité Européenne, "European conformity" in French.               |     |  |  |  |  |

|               | FCC Part 15 Class B was used for Evolution of United States (US) Emission |     |  |  |  |  |

|               | Standards for Commercial Electronic Products, The United States (US)      |     |  |  |  |  |

| <b>HC</b>     | covers all types of unintentional radiators under Subparts A and B        | Yes |  |  |  |  |

|               | (Sections 15.1 through 15.199) of FCC 47 CFR Part 15, usually called just |     |  |  |  |  |

|               | FCC Part 15                                                               |     |  |  |  |  |

# 3.0 SATA SSD Pin Assignment

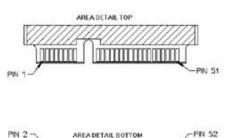

### **3.1 Pin Location**

The following figure shows the pin location of the mSATA, the connector is with both signal and power segments.

### 3.2 Pin Assignment

There are total of 52 pin and the pin definitions are shown in Table 3-1

Table 3-1

| Pin No. | Function | Description            |  |  |  |  |

|---------|----------|------------------------|--|--|--|--|

| P1      | Reserved | No Connect             |  |  |  |  |

| P2      | +3.3V    | 3.3V Source            |  |  |  |  |

| Р3      | Reserved | No Connect             |  |  |  |  |

| P4      | GND      | Return Current Path    |  |  |  |  |

| Р5      | Reserved | No Connect             |  |  |  |  |

| P6      | +1.5V    | Not used in ATP design |  |  |  |  |

| P7      | Reserved | No Connect             |  |  |  |  |

| Р8      | Reserved | No Connect             |  |  |  |  |

| Р9      | GND      | Return Current Path    |  |  |  |  |

| P10     | Reserved | No Connect             |  |  |  |  |

| P11     | Reserved | No Connect             |  |  |  |  |

| P12     | Reserved | No Connect             |  |  |  |  |

| P13     | Reserved | No Connect             |  |  |  |  |

| P14     | Reserved | No Connect             |  |  |  |  |

| P15     | GND      | Return Current Path    |  |  |  |  |

| P16     | Reserved | No Connect             |  |  |  |  |

| P17     | Reserved | No Connect             |  |  |  |  |

| P18     | GND      | Return Current Path    |  |  |  |  |

| P19     | Reserved | No Connect             |  |  |  |  |

Version 1.0

| P20ReservedNo ConnectP21GNDReturn Current PathP22ReservedNo ConnectP23+BHost Receiver Differential Signal PairP24+3.3V3.3V SourceP25-BHost Receiver Differential Signal PairP26GNDReturn Current PathP27GNDReturn Current PathP28+1.5VNot used in ATP designP29GNDReturn Current PathP29GNDReturn Current PathP30Two Wire<br>InterfaceTwo Wire interface Clock <sup>3</sup> P31-AHost Transmitter Differential Signal PairP32Two Wire<br>InterfaceTwo Wire interface Data <sup>3</sup> P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP38ReservedNo ConnectP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedNo ConnectP44ReservedNo ConnectP45VenderNot used in ATP design <sup>2</sup> P46ReservedNo ConnectP47VenderNot used in ATP designP48+1.5VNot used in ATP designP49DAS/DSSDevice A                                                                                                                                           | Pin No. | Function  | Description                                         |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------|-----------------------------------------------------|--|--|--|

| P22ReservedNo ConnectP23+BHost Receiver Differential Signal PairP24+3.3V3.3V SourceP25-BHost Receiver Differential Signal PairP26GNDReturn Current PathP27GNDReturn Current PathP28+1.5VNot used in ATP designP29GNDReturn Current PathP30Two Wire<br>InterfaceTwo Wire interface Clock <sup>3</sup> P31-AHost Transmitter Differential Signal PairP32Two Wire<br>InterfaceTwo Wire interface Data <sup>3</sup> P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedShall be a No ConnectP43ReservedShall be a No ConnectP43ReservedShall be a No ConnectP44ReservedNot used in ATP design <sup>2</sup> P46ReservedNot used in ATP designP47VenderNot used in ATP design <sup>2</sup> P46ReservedNot used in ATP designP47VenderNot used in ATP designP48+1.5VNot used in ATP designP49DAS/DSSDevice Activity Signal / Disable Staggered Spin-up <td>P20</td> <td>Reserved</td> <td colspan="3">No Connect</td> | P20     | Reserved  | No Connect                                          |  |  |  |

| P23+BHost Receiver Differential Signal PairP24+3.3V3.3V SourceP25-BHost Receiver Differential Signal PairP26GNDReturn Current PathP27GNDReturn Current PathP28+1.5VNot used in ATP designP29GNDReturn Current PathP30Two Wire<br>InterfaceTwo Wire interface Clock <sup>3</sup> P31-AHost Transmitter Differential Signal PairP32Two Wire<br>InterfaceTwo Wire interface Data <sup>3</sup> P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedShall be a No ConnectP44ReservedShall be a No ConnectP45VenderNot used in ATP design <sup>2</sup> P46ReservedNo ConnectP47VenderNot used in ATP designP48+1.5VNot used in ATP designP49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohmP51venderShall be pulled to GND by a 0 ohm                                                                  | P21     | GND       | Return Current Path                                 |  |  |  |

| P24+3.3V3.3V SourceP25-BHost Receiver Differential Signal PairP26GNDReturn Current PathP27GNDReturn Current PathP28+1.5VNot used in ATP designP29GNDReturn Current PathP30Two Wire<br>InterfaceTwo Wire interface Clock <sup>3</sup> P31-AHost Transmitter Differential Signal PairP32Two Wire<br>InterfaceTwo Wire interface Data <sup>3</sup> P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedShall be a No ConnectP44ReservedShall be a No ConnectP45VenderNot used in ATP design <sup>2</sup> P46ReservedNo ConnectP47VenderNot used in ATP design <sup>2</sup> P48+1.5VNot used in ATP designP49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device <sup>1</sup>                                                                                                      | P22     | Reserved  | No Connect                                          |  |  |  |

| P25-BHost Receiver Differential Signal PairP26GNDReturn Current PathP27GNDReturn Current PathP28+1.5VNot used in ATP designP29GNDReturn Current PathP30Two Wire<br>InterfaceTwo Wire interface Clock <sup>3</sup> P31-AHost Transmitter Differential Signal PairP32Two Wire<br>InterfaceTwo Wire interface Data <sup>3</sup> P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedShall be a No ConnectP44ReservedEnter/Exit DevSleepP45VenderNot used in ATP design <sup>2</sup> P46ReservedNo ConnectP47VenderNot used in ATP designP48+1.5VNot used in ATP designP49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohmP51PresenceShall be pulled to GND by a 0 ohm to 220 ohmP51PresenceShall be pulled to GND to metore <sup>1</sup>                                                             | P23     | +B        | Host Receiver Differential Signal Pair              |  |  |  |

| P26GNDReturn Current PathP27GNDReturn Current PathP28+1.5VNot used in ATP designP29GNDReturn Current PathP30Two Wire<br>InterfaceTwo Wire interface Clock <sup>3</sup> P31-AHost Transmitter Differential Signal PairP32Two Wire<br>InterfaceTwo Wire interface Data <sup>3</sup> P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedNo ConnectP44ReservedShall be a No ConnectP45VenderNot used in ATP design <sup>2</sup> P46ReservedNo ConnectP47VenderNot used in ATP designP48+1.5VNot used in ATP designP49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohmP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm                                                                                                                                                                         | P24     | +3.3V     | 3.3V Source                                         |  |  |  |

| P27GNDReturn Current PathP28+1.5VNot used in ATP designP29GNDReturn Current PathP30Two Wire<br>InterfaceTwo Wire interface Clock <sup>3</sup> P31-AHost Transmitter Differential Signal PairP32Two Wire<br>InterfaceTwo Wire interface Data <sup>3</sup> P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedNo ConnectP44ReservedShall be a No Connect on mSATA Devices <sup>4</sup> P44ReservedShall be a No ConnectP45VenderNot used in ATP design <sup>2</sup> P46ReservedNo ConnectP47VenderNot used in ATP design <sup>2</sup> P48+1.5VNot used in ATP design <sup>2</sup> P49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device <sup>1</sup>                                                                                                                           | P25     | -В        | Host Receiver Differential Signal Pair              |  |  |  |

| P28+1.5VNot used in ATP designP29GNDReturn Current PathP30Two Wire<br>InterfaceTwo Wire interface Clock3P31-AHost Transmitter Differential Signal PairP32Two Wire<br>InterfaceTwo Wire interface Data3P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedNo ConnectP44ReservedShall be a No Connect on mSATA Devices4P44ReservedNot used in ATP design 2P46ReservedNot used in ATP design 2P48+1.5VNot used in ATP design 2P48+1.5VNot used in ATP design 2P49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device1                                                                                                                                                                                                                                                            | P26     | GND       | Return Current Path                                 |  |  |  |

| P29GNDReturn Current PathP30Two Wire<br>InterfaceTwo Wire interface Clock3P31-AHost Transmitter Differential Signal PairP32Two Wire<br>InterfaceTwo Wire interface Data3P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedNo ConnectP44ReservedShall be a No Connect on mSATA Devices4P44ReservedNot used in ATP design 2P45VenderNot used in ATP design 2P46ReservedNot used in ATP design 2P47VenderNot used in ATP design 2P48+1.5VNot used in ATP design 2P49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device4                                                                                                                                                                                                                                                        | P27     | GND       | Return Current Path                                 |  |  |  |

| P30Two Wire<br>InterfaceTwo Wire interface Clock3P31-AHost Transmitter Differential Signal PairP32Two Wire<br>InterfaceTwo Wire interface Data3P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedNo ConnectP44ReservedShall be a No Connect on mSATA Devices4P44ReservedEnter/Exit DevSleepP45VenderNot used in ATP design2P48+1.5VNot used in ATP design4P49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51Detectionresistor on device3                                                                                                                                                                                                                                                                                                                                                                                                           | P28     | +1.5V     | Not used in ATP design                              |  |  |  |

| P30Two Wire interface Clock3P31-AHost Transmitter Differential Signal PairP32Two Wire<br>InterfaceTwo Wire interface Data3P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedNo ConnectP44ReservedShall be a No ConnectP45VenderNot used in ATP design2P46ReservedNo ConnectP47VenderNot used in ATP design2P48+1.5VNot used in ATP design2P49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51Detectionresistor on device3                                                                                                                                                                                                                                                                                                                                                                                                                           | P29     | GND       | Return Current Path                                 |  |  |  |

| P31-AHost Transmitter Differential Signal PairP32Two Wire<br>InterfaceTwo Wire interface Data3P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedNo ConnectP44ReservedShall be a No Connect on mSATA Devices4P45VenderNot used in ATP design2P46ReservedNot used in ATP design2P48+1.5VNot used in ATP design2P49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device4                                                                                                                                                                                                                                                                                                                                                                                                         | P30     | Two Wire  | Two Wire interface Clock <sup>3</sup>               |  |  |  |

| P32Two Wire<br>InterfaceTwo Wire interface Data <sup>3</sup> P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedNo ConnectP44ReservedShall be a No Connect on mSATA Devices <sup>4</sup> P44ReservedShall be a No Connect on mSATA Devices <sup>4</sup> P45VenderNot used in ATP design <sup>2</sup> P46ReservedNot used in ATP design <sup>2</sup> P48+1.5VNot used in ATP design <sup>2</sup> P49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device <sup>1</sup>                                                                                                                                                                                                                                                                                                           |         | Interface |                                                     |  |  |  |

| P32InterfaceTwo Wire interface Data <sup>3</sup> P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedNo ConnectP44ReservedShall be a No Connect on mSATA Devices <sup>4</sup> P45VenderNot used in ATP design <sup>2</sup> P46ReservedNot used in ATP design <sup>2</sup> P48+1.5VNot used in ATP designP49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohmP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm                                                                                                                                                                                                                                                                                                                                                                                | P31     | -A        | Host Transmitter Differential Signal Pair           |  |  |  |

| P33+AHost Transmitter Differential Signal PairP34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedNo ConnectP44ReservedShall be a No Connect on mSATA Devices <sup>4</sup> P44ReservedShall be a No Connect on mSATA Devices <sup>4</sup> P44ReservedNot used in ATP design <sup>2</sup> P45VenderNot used in ATP design <sup>2</sup> P46ReservedNot used in ATP designP47VenderNot used in ATP designP48+1.5VNot used in ATP designP49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device <sup>1</sup>                                                                                                                                                                                                                                                                                                                      | P32     | Two Wire  | Two Wire interface Data <sup>3</sup>                |  |  |  |

| P34GNDReturn Current PathP35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedNo ConnectP44ReservedShall be a No Connect on mSATA Devices <sup>4</sup> P44ReservedShall be a No Connect on mSATA Devices <sup>4</sup> P45VenderNot used in ATP design <sup>2</sup> P46ReservedNo ConnectP47VenderNot used in ATP design <sup>2</sup> P48+1.5VNot used in ATP designP49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                 |         | Interface |                                                     |  |  |  |

| P35GNDReturn Current PathP36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedNo Connect on mSATA Devices <sup>4</sup> P44ReservedShall be a No Connect on mSATA Devices <sup>4</sup> P45VenderNot used in ATP design 2P46ReservedNo ConnectP47VenderNot used in ATP design 2P48+1.5VNot used in ATP design 2P49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P33     | +A        | Host Transmitter Differential Signal Pair           |  |  |  |

| P36ReservedNo ConnectP37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedNo ConnectP44ReservedShall be a No Connect on mSATA Devices <sup>4</sup> P45VenderNot used in ATP design 2P46ReservedNot used in ATP design 2P47VenderNot used in ATP design 2P48+1.5VNot used in ATP design 2P49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P34     | GND       | Return Current Path                                 |  |  |  |

| P37GNDReturn Current PathP38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedShall be a No Connect on mSATA Devices <sup>4</sup> P44ReservedEnter/Exit DevSleepP45VenderNot used in ATP design 2P46ReservedNo ConnectP47VenderNot used in ATP design 2P48+1.5VNot used in ATP designP49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P35     | GND       | Return Current Path                                 |  |  |  |

| P38ReservedNo ConnectP39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedShall be a No Connect on mSATA Devices <sup>4</sup> P44ReservedShall be a No Connect on mSATA Devices <sup>4</sup> P45VenderNot used in ATP design <sup>2</sup> P46ReservedNo ConnectP47VenderNot used in ATP design <sup>2</sup> P48+1.5VNot used in ATP designP49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P36     | Reserved  | No Connect                                          |  |  |  |

| P39+3.3V3.3V SourceP40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedShall be a No Connect on mSATA Devices <sup>4</sup> P44ReservedEnter/Exit DevSleepP45VenderNot used in ATP design 2P46ReservedNot connectP47VenderNot used in ATP design 2P48+1.5VNot used in ATP design 2P49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | P37     | GND       | Return Current Path                                 |  |  |  |

| P40GNDReturn Current PathP41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedShall be a No Connect on mSATA Devices4P44ReservedEnter/Exit DevSleepP45VenderNot used in ATP design2P46ReservedNo ConnectP47VenderNot used in ATP design2P48+1.5VNot used in ATP design2P49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | P38     | Reserved  | No Connect                                          |  |  |  |

| P41+3.3V3.3V SourceP42ReservedNo ConnectP43ReservedShall be a No Connect on mSATA Devices4P44ReservedEnter/Exit DevSleepP45VenderNot used in ATP design2P46ReservedNot used in ATP design2P47VenderNot used in ATP design2P48+1.5VNot used in ATP design2P49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | P39     | +3.3V     | 3.3V Source                                         |  |  |  |

| P42ReservedNo ConnectP43ReservedShall be a No Connect on mSATA Devices4P44ReservedEnter/Exit DevSleepP45VenderNot used in ATP design2P46ReservedNot used in ATP design2P47VenderNot used in ATP design2P48+1.5VNot used in ATP design2P49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | P40     | GND       | Return Current Path                                 |  |  |  |

| P43ReservedShall be a No Connect on mSATA Devices4P44ReservedEnter/Exit DevSleepP45VenderNot used in ATP design2P46ReservedNo ConnectP47VenderNot used in ATP design2P48+1.5VNot used in ATP design2P49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P41     | +3.3V     | 3.3V Source                                         |  |  |  |

| P44ReservedEnter/Exit DevSleepP45VenderNot used in ATP design 2P46ReservedNo ConnectP47VenderNot used in ATP design 2P48+1.5VNot used in ATP designP49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P42     | Reserved  | No Connect                                          |  |  |  |

| P45VenderNot used in ATP design2P46ReservedNo ConnectP47VenderNot used in ATP design2P48+1.5VNot used in ATP designP49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P43     | Reserved  | Shall be a No Connect on mSATA Devices <sup>4</sup> |  |  |  |

| P46ReservedNo ConnectP47VenderNot used in ATP design 2P48+1.5VNot used in ATP designP49DAS/DSSDevice Activity Signal / Disable Staggered Spin-upP50GNDReturn Current PathP51PresenceShall be pulled to GND by a 0 ohm to 220 ohm<br>resistor on device1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P44     | Reserved  | Enter/Exit DevSleep                                 |  |  |  |

| P47   Vender   Not used in ATP design <sup>2</sup> P48   +1.5V   Not used in ATP design     P49   DAS/DSS   Device Activity Signal / Disable Staggered Spin-up     P50   GND   Return Current Path     P51   Presence   Shall be pulled to GND by a 0 ohm to 220 ohm     P51   Option   resistor on device <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P45     | Vender    | Not used in ATP design <sup>2</sup>                 |  |  |  |

| P48   +1.5V   Not used in ATP design     P49   DAS/DSS   Device Activity Signal / Disable Staggered Spin-up     P50   GND   Return Current Path     P51   Presence   Shall be pulled to GND by a 0 ohm to 220 ohm     P51   Detection   resistor on device <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | P46     | Reserved  | No Connect                                          |  |  |  |

| P49 DAS/DSS Device Activity Signal / Disable Staggered Spin-up   P50 GND Return Current Path   P51 Presence Shall be pulled to GND by a 0 ohm to 220 ohm   P51 Detection resistor on device <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | P47     | Vender    | Not used in ATP design <sup>2</sup>                 |  |  |  |

| P50 GND Return Current Path   P51 Presence Shall be pulled to GND by a 0 ohm to 220 ohm   Detection resistor on device <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P48     | +1.5V     | Not used in ATP design                              |  |  |  |

| P51 Presence Shall be pulled to GND by a 0 ohm to 220 ohm<br>Detection resistor on device <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P49     | DAS/DSS   | Device Activity Signal / Disable Staggered Spin-up  |  |  |  |

| P51 Detection resistor on device <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P50     | GND       | Return Current Path                                 |  |  |  |

| Detection resistor on device <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | Presence  | Shall be pulled to GND by a 0 ohm to 220 ohm        |  |  |  |

| P52 +3.3V 3.3V Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P51     | Detection | resistor on device <sup>1</sup>                     |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | P52     | +3.3V     | 3.3V Source                                         |  |  |  |

Notes:

1. Presence detection pin indicates presence of an mSATA device.

2. No connect on the host side.

3. Pins 30 and 32 are intended for use as a two wire interface to read a memory device to determine device information (an example of this would be for use as SMB bus pins). These pins are not designed to be active in conjunction with the SATA signal differential pairs. Not used in ATP design.

4. P43 to be a no connect on mSATA devices. Given that non-mSATA devices ground P43, configurable shared-socket designs may use this pin to identify mSATA and non-mSATA devices.

# 4.0 Command Set

### 4.1 ATA Command Set

ATP mSATA support the commands show in the following table

| Table 4-1                   |            |                   |  |  |  |  |

|-----------------------------|------------|-------------------|--|--|--|--|

| Command                     | Code       | Protocol          |  |  |  |  |

| General Feature Set         |            |                   |  |  |  |  |

| Execute Drive Diagnostic    | 90h        | Device diagnostic |  |  |  |  |

| Flush Cache                 | E7h        | Non-data          |  |  |  |  |

| Flush Cache Ext             | EAh        | Non-data          |  |  |  |  |

| Identify Device             | ECh        | PIO data-in       |  |  |  |  |

| Initialize Drive Parameters | 91h        | Non-data          |  |  |  |  |

| Read DMA                    | C8h        | DMA               |  |  |  |  |

| Read DMA Ext                | 25h        | DMA               |  |  |  |  |

| Read Log Ext                | 2Fh        | PIO data-in       |  |  |  |  |

| Read Multiple               | C4h        | PIO data-in       |  |  |  |  |

| Read Sector(s)              | 20h or 21h | PIO data-in       |  |  |  |  |

| Read Sector(s) Ext          | 24h        | PIO data-in       |  |  |  |  |

| Read Verify Sector(s)       | 40h or 41h | Non-data          |  |  |  |  |

| Read Verify Sector(s) Ext   | 42h        | Non-data          |  |  |  |  |

| Set Feature                 | EFh        | Non-data          |  |  |  |  |

| Set Multiple Mode           | C6h        | Non-data          |  |  |  |  |

| Write DMA                   | CAh        | DMA               |  |  |  |  |

| Write DMA Ext               | 35h        | DMA               |  |  |  |  |

| Write DMA Fua Ext           | 3Dh        | DMA               |  |  |  |  |

| Write Log Ext               | 3Fh        | PIO data-out      |  |  |  |  |

| Write Multiple              | C5h        | PIO data-out      |  |  |  |  |

| Write Sector(s)             | 30h or 31h | PIO data-out      |  |  |  |  |

| Write Sector(s) Ext         | 34h        | PIO data-out      |  |  |  |  |

Table 4-1

#### ATP mSATA Embedded Module Specification

Version 1.0

| NOP                                 | 00h        | Non-data         |  |

|-------------------------------------|------------|------------------|--|

| Read Buffer                         | E4h        | PIO data-in      |  |

| Write Buffer                        | E8h        | PIO data-out     |  |

| Data Set Management                 | 06h        | DMA PIO data-out |  |

| Download Microcode                  | 92h        |                  |  |

| Power Management Feature Set        |            |                  |  |

| Check Power Mode                    | E5h or 98h | Non-data         |  |

| Idle                                | E3h or 97h | Non-data         |  |

| Idle Immediate                      | E1h or 95h | Non-data         |  |

| Sleep                               | E6h or 99h | Non-data         |  |

| Standby                             | E2h or 96h | Non-data         |  |

| Standby Immediate                   | E0h or 94h | Non-data         |  |

| Security Mode Feature Set           |            |                  |  |

| Security Set Password               | F1h        | PIO data-out     |  |

| Security Unlock                     | F2h        | PIO data-out     |  |

| Security Erase Prepare              | F3h        | Non-data         |  |

| Security Erase Unit                 | F4h        | PIO data-out     |  |

| Security Freeze Lock                | F5h        | Non-data         |  |

| Security Disable Password           | F6h        | PIO data-out     |  |

| SMART Feature Set                   |            |                  |  |

| SMART Disable Operation             | B0h        | Non-data         |  |

| SMART Enable/Disable Autosave       | B0h        | Non-data         |  |

| SMART Enable Operations             | B0h        | Non-data         |  |

| SMART Return Status                 | B0h        | Non-data         |  |

| SMART Execute Off-Line<br>Immediate | B0h        | Non-data         |  |

| SMART Read Data                     | B0h        | PIO data-in      |  |

| SMART Read Threshold                | B0h        | PIO data-in      |  |

| SMART Read Log                      | B0h        | PIO data-in      |  |

| SMART Write Log                     | B0h        | PIO data-out     |  |

| SMART Save Attribute Values         | B0h        | Non-data         |  |

| Host Protected Area Feature Set     |            |                  |  |

| Read Native Max Address             | F8h        | Non-data         |  |

| Read Native Max Address Ext         | 27h        | Non-data         |  |

| Set Max Address                     | F9h        | Non-data         |  |

| Set Max Address Ext                 | 37h        | Non-data         |  |

| Set Max Set Password                | F9h        | PIO data-out     |  |

| Set Max Lock                        | F9h        | Non-data         |  |

ATP Confidential © ATP Electronics, Inc.

Version 1.0

| Set Max Freeze Lock | F9h | Non-data     |  |

|---------------------|-----|--------------|--|

| Set Max Unlock      | F9h | PIO data-out |  |

# 4.2 Identity Device Data

| -               | Table 4-2     |                                                                             |  |  |  |  |  |

|-----------------|---------------|-----------------------------------------------------------------------------|--|--|--|--|--|

| Word<br>Address | Default Value | Data Field Type Information                                                 |  |  |  |  |  |

| 0               | 0040h         | General Configuration                                                       |  |  |  |  |  |

| 1               | XXXXh         | Default number of cylinders                                                 |  |  |  |  |  |

| 2               | 0000h         | Reserved                                                                    |  |  |  |  |  |

| 3               | 00XXh         | Default number of heads                                                     |  |  |  |  |  |

| 4               | 0000h         | Obsolete                                                                    |  |  |  |  |  |

| 5               | 0240h         | Obsolete                                                                    |  |  |  |  |  |

| 6               | XXXXh         | Default number of sectors per track                                         |  |  |  |  |  |

| 7-8             | XXXXh         | Number of sectors per card<br>(Word 7 = MSW, Word 8 = LSW)                  |  |  |  |  |  |

| 9               | 0000h         | Obsolete                                                                    |  |  |  |  |  |

| 10-19           | XXXXh         | Serial number in ASCII (Left justified) with 12 or less characters          |  |  |  |  |  |

| 20              | 0002h         | Obsolete                                                                    |  |  |  |  |  |

| 21              | 0002h         | Obsolete                                                                    |  |  |  |  |  |

| 22              | 0000h         | Obsolete                                                                    |  |  |  |  |  |

| 23-26           | XXXXh         | Firmware revision in ASCII (Left justified). Big Endian Byte Order in Word  |  |  |  |  |  |

| 27-41           | XXXXh         | Model number in ASCII (Left justified). Big Endian Byte Order in Word       |  |  |  |  |  |

| 42~46           |               | Part number in ASCII (Right justified) preceded by the ANSI space character |  |  |  |  |  |

| 47              | 8001h         | Maximum number of sectors on Read/Write Multiple command                    |  |  |  |  |  |

| 48              | 0000h         | Reserved                                                                    |  |  |  |  |  |

| 49              | 0F00h         | Capabilities                                                                |  |  |  |  |  |

| 50              | 4000h         | Capabilities                                                                |  |  |  |  |  |

| 51              | 0200h         | PIO data transfer cycle timing mode                                         |  |  |  |  |  |

| 52              | 0000h         | Obsolete                                                                    |  |  |  |  |  |

| 53              | 0007h         | Field validity                                                              |  |  |  |  |  |

| 54              | XXXXh         | Current numbers of cylinders                                                |  |  |  |  |  |

| 55              | XXXXh         | Current numbers of heads                                                    |  |  |  |  |  |

| 56              | XXXXh         | Current sectors per track                                                   |  |  |  |  |  |

| Ve  | rsion  | 1.0 |

|-----|--------|-----|

| • • | 101011 | ±.0 |

| 57-58 | XXXXh  | Current capacity in sectors (LBAs)<br>(Word57=LSW, Word58=MSW) |  |  |  |

|-------|--------|----------------------------------------------------------------|--|--|--|

| 59    | 0101h  | Multiple sector setting                                        |  |  |  |

| 60.64 |        | Total number of user addressable logical sectors for 28-bit    |  |  |  |

| 60-61 | XXXXh  | commands (DWord)                                               |  |  |  |

| 62    | 0000h  | Reserved                                                       |  |  |  |

| 62    | 0207h  | Multiword DMA transfer                                         |  |  |  |

| 63    | 0207h  | Supports MDMA Mode 0, 1, and 2                                 |  |  |  |

| 64    | 0003h  | Advanced PIO modes supported                                   |  |  |  |

| 65    | 0078h  | Minimum Multiword DMA transfer cycle time per word             |  |  |  |

| 66    | 0078h  | Recommended Multiword DMA transfer cycle time                  |  |  |  |

| 67    | 0078h  | Minimum PIO transfer cycle time without flow control           |  |  |  |

| 68    | 0078h  | Minimum PIO transfer cycle time with IORDY flow control        |  |  |  |

| 69    | 4000h  | Additional supported                                           |  |  |  |

| 70~74 | 0000h  | Reserved                                                       |  |  |  |

| 75    | 0031   | Queue depth                                                    |  |  |  |

|       |        | Serial ATA capabilities                                        |  |  |  |

|       |        | Support Serial ATA Gen1                                        |  |  |  |

|       |        | Support Serial ATA Gen2                                        |  |  |  |

| 76    | 030E   | Support Serial ATA Gen3                                        |  |  |  |

| 70    | 0301   | Supports Phy event counters log                                |  |  |  |

|       |        | Support receipt of host-initiated interface power management   |  |  |  |

|       |        | requests                                                       |  |  |  |

|       |        | Supports Native Command Queuing                                |  |  |  |

| 77    | 0080h  | Serial ATA additional capability                               |  |  |  |

|       | 008011 | DevSleep_to_ReducedPwerState                                   |  |  |  |

|       |        | Serial ATA features supported                                  |  |  |  |

| 78    | 044C   | Supports Device Sleep                                          |  |  |  |

| /0    | 0440   | Supports software settings preservation                        |  |  |  |

|       |        | Device supports initiating power management                    |  |  |  |

| 79    | 0040h  | Reserved                                                       |  |  |  |

| 80    | 03F0h  | Major version number (ACS-2)                                   |  |  |  |

| 81    | 0000h  | Minor version number                                           |  |  |  |

| 82    | 742Bh  | Command sets supported 0                                       |  |  |  |

| 83    | 7500h  | Command sets supported 1                                       |  |  |  |

| 84    | 4023h  | Command sets supported 2                                       |  |  |  |

| 85~87 | XXXXh  | Command set/feature enabled                                    |  |  |  |

| 88    | 007Fh  | Ultra DMA supported and selected                               |  |  |  |

|       |        |                                                                |  |  |  |

Version 1.0

| 89      | 0003h  | Time required for Normal Erase mode Security Erase Unit            |  |  |  |  |

|---------|--------|--------------------------------------------------------------------|--|--|--|--|

| 05      | 000511 | command                                                            |  |  |  |  |

| 90      | 0001h  | Time required for Enhanced Erase mode Security Erase Unit          |  |  |  |  |

| 50      | 000111 | command                                                            |  |  |  |  |

| 91      | 0000h  | Current advanced power management value                            |  |  |  |  |

| 92      | FFFEh  | Master password identifier                                         |  |  |  |  |

| 93~99   | 0000h  | Reserved                                                           |  |  |  |  |

| 100~103 | XXXXh  | Maximum user LBA for 48-bit address feature set                    |  |  |  |  |

| 104     | 0000h  | Reserved                                                           |  |  |  |  |

| 105     | 0100h  | Maximum number of 512-byte blocks per Data Set Management          |  |  |  |  |

| 105     | 010011 | command                                                            |  |  |  |  |

|         |        | bit 12 = 1 to indicate that the Logical Sector Size field is valid |  |  |  |  |

| 106     | 5000   | Bit 14 = 1                                                         |  |  |  |  |

|         |        | Bit 15 = 0                                                         |  |  |  |  |

| 107~116 | 0000h  | Reserved                                                           |  |  |  |  |

| 117~118 | 0x800  | Logical sector size                                                |  |  |  |  |

| 119~127 | 0000h  | Reserved                                                           |  |  |  |  |

| 128     | 0001h  | Security status                                                    |  |  |  |  |

| 129~159 | XXXXh  | Vendor specific                                                    |  |  |  |  |

| 160     | 0000h  | Power requirement description                                      |  |  |  |  |

| 161     | 0000h  | Reserved                                                           |  |  |  |  |

| 162     | 0000h  | Key management schemes supported                                   |  |  |  |  |

| 163     | 0000h  | CF Advanced True IDE Timing Mode Capability and Setting            |  |  |  |  |

| 164~168 | 0000h  | Reserved                                                           |  |  |  |  |

| 169     | 0001h  | Data Set Management supported                                      |  |  |  |  |

| 170~216 | XXXXh  | Reserved                                                           |  |  |  |  |

| 217     | 0001h  | Non-rotating media(SSD)                                            |  |  |  |  |

| 218~221 | 0000h  | Reserved                                                           |  |  |  |  |

| 222     | 107Fh  | Transport major revision (SATA Rev 3.1)                            |  |  |  |  |

| 223~254 | 0000h  | Reserved                                                           |  |  |  |  |

| 255     | XXXXh  | Integrity word                                                     |  |  |  |  |

|         |        |                                                                    |  |  |  |  |

### 4.3 Smart Information

ATP mSATA supports S.M.A.R.T. ATA feature set in IDE mode, AHCI mode, not support in RAID mode.

### 4.3.1 Smart Subcommand Sets

In order to select a subcommand the host must write the subcommand code to the device's

Features Register before issuing the SMART Function Set command. The subcommands are

listed below.

| Command                          | Command Code |

|----------------------------------|--------------|

| SMART READ DATA                  | D0h          |

| SMART READ ATTRIBUTE THRESHOLD   | D1h          |

| SMART ENABLE/DISABLE AUTOSAVE    | D2h          |

| SMART SAVE ATTRIBUTE VALUES      | D3h          |

| SMART EXECUTE OFF-LINE IMMIDIATE | D4h          |

| READ LOG                         | D5h          |

| WRITE LOG                        | D6h          |

| SMART ENABLE OPERATIONS          | D8h          |

| SMART DISABLE OPERATIONS         | D9h          |

| SMART RETURN STATUS              | DAh          |

#### Table 4-3

Note: If the reserved size is below a threshold, status can be read from the Cylinder Register using the Return Status command (DAh)

### 4.3.2 SMART Read Data (Subcommand Doh)

The following 512 bytes make up the device SMART data structure. Users can obtain the data using the "Read Data" command (D0h).

| Byte      | F/V | Description                                                         |  |  |  |  |

|-----------|-----|---------------------------------------------------------------------|--|--|--|--|

| 0~1       | Х   | Revision code                                                       |  |  |  |  |

| 2~361     | Х   | Vendor Specific                                                     |  |  |  |  |

| 362       | V   | Off-line data collection status                                     |  |  |  |  |

| 363       | Х   | Self-test execution status byte                                     |  |  |  |  |

| 364~365 V |     | Total time in seconds to complete off-line data collection activity |  |  |  |  |

#### Table 4-4

| 366     | Х | Vendor Specific                                       |  |  |  |

|---------|---|-------------------------------------------------------|--|--|--|

| 367     | F | Off-line data collection capability                   |  |  |  |

| 368~369 | F | SMART capability                                      |  |  |  |

|         |   | Error logging capability:                             |  |  |  |

| 370     | F | 7-1 = Reserved                                        |  |  |  |